# Performance Investigation of Cascaded Multilevel Inverter and Dual Inverter using SVPWM technique

|                                                                                                                                                                                       |                                                                                                                                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>D.Muruganandhan,</b><br><b>Electrical &amp; Electronics Engineering</b><br><b>Pondicherry University</b><br><b>Manakula Vinayagar Institute of Technology</b><br><b>Puducherry</b> | <b>S. Punitha,</b><br><b>Electrical &amp; Electronics Engineering</b><br><b>Pondicherry University</b><br><b>Sri Vengateshwara College Of Engineering &amp; Technology</b><br><b>Puducherry</b> |

| <b>R.Muthunagai</b><br><b>Electrical &amp; Electronics Engineering</b><br><b>Pondicherry University</b><br><b>Manakula Vinayagar Institute of Technology</b><br><b>Puducherry</b>     | <b>M.Murali</b><br><b>Electrical &amp; Electronics Engineering</b><br><b>Pondicherry University</b><br><b>Sri Vengateshwara College Of Engineering &amp; Technology</b><br><b>Puducherry</b>    |

## ABSTRACT

In this paper, the performance investigation approach for multilevel inverter (MLI) and Dual Inverter (DI) using space vector pulse width modulation (SVPWM) technique is modeled using Simulink/Matlab environment. A novel switching technique using the Embedded Matlab editor results in a higher magnitude of fundamental output voltage available as compared to the sinusoidal PWM. A Simulation model is carried out for the novel switching SVPWM scheme in the Embedded Matlab Editor and the generated firing pulses are applied to the Multilevel Inverter fed induction motor drive and Dual Inverter fed open end winding induction motor drive.

## 1. INTRODUCTION

The speed control of Induction motor has got a lot of importance in industrial applications. Stator voltage speed control is the most commonly used method. Stator voltage of induction motor is conventionally controlled by using the conventional PWM inverters. Later development is MLI; it allows the operation at higher DC voltages using semiconductor switches connected in series and produce voltage waveforms with better harmonic profile than conventional two level inverters [1-5]. The drawback of MLI configuration is complex for higher number of levels and in turn affects the cost of the system clearly. The drawback of MLI is overcome by feeding the induction motor from both the ends through two three phase inverters with the removal of neutral point of stator. This configuration is called Dual inverter fed open end winding induction motor drive. The advantages of the dual inverter are, it uses less number of switches therefore it does not have any switching losses, absence of neutral point fluctuations, less number of DC voltage sources, it achieves improved quality of output waveform and reduced system complexity and cost [6-8]. Further it provides output with less THD by increasing the number of output levels when compared to the MLI of same levels. In this paper the performance investigation approach for Multilevel inverter and Dual Inverter using Space vector pulse width modulation technique is modeled using Simulink/Matlab environment.

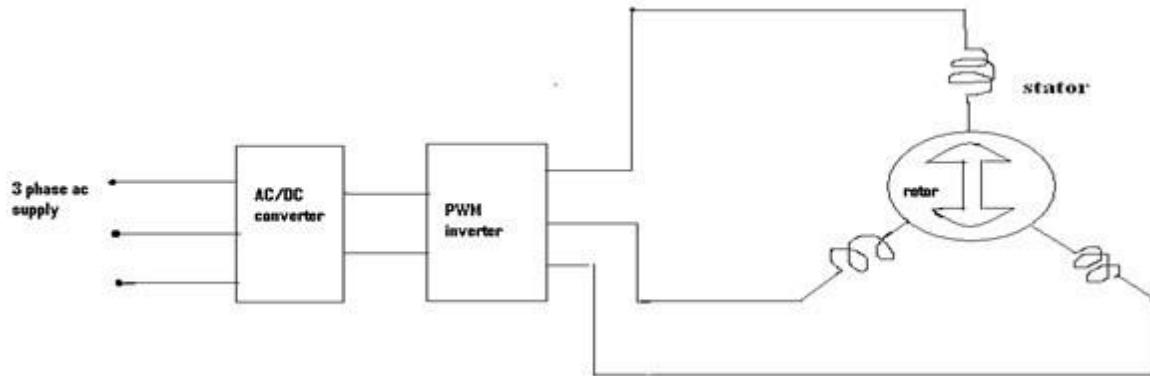

### 1.1 Conventional PWM Inverter for Induction Motor Drive

Conventionally PWM inverter is connected to the motor. When increasing the levels of the inverter THD is high. In general, a pulse width-modulation (PWM) inverter generates high-frequency common mode voltage at motor terminals, which results in unwanted leakage current. This unwanted common-mode current may cause premature bearing failure, as well as electromagnetic interferences disturbing neighboring electronic devices. Hence, it is necessary to eliminate the common mode voltage. Figure 1 shows the PWM Inverter for Induction Motor Drive.

Figure 1 PWM Inverter for Induction Motor Drive

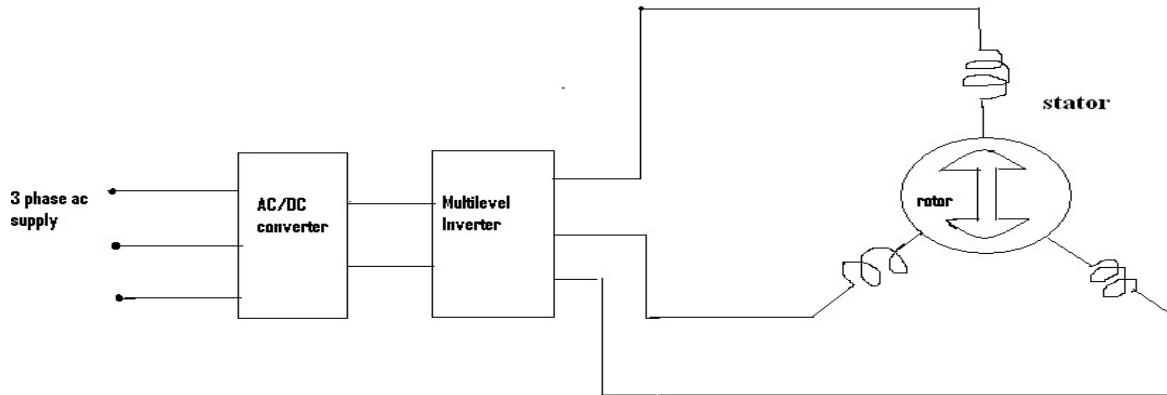

### 1.2 Multilevel Inverter (MLI) for Induction Motor Drive

Cascaded H-bridge inverters are widely used for induction motor control application. By cascading many H-bridges for achieving lower Total Harmonic Distortion (THD), the circuit complexity and cost increases. No of Output levels is  $2s+1$ , where  $s$  is No of bridge per phase. Figure 2 depicts the Multilevel Inverter (MLI) for Induction Motor Drive

Figure 2 Multilevel Inverter (MLI) for Induction Motor Drive

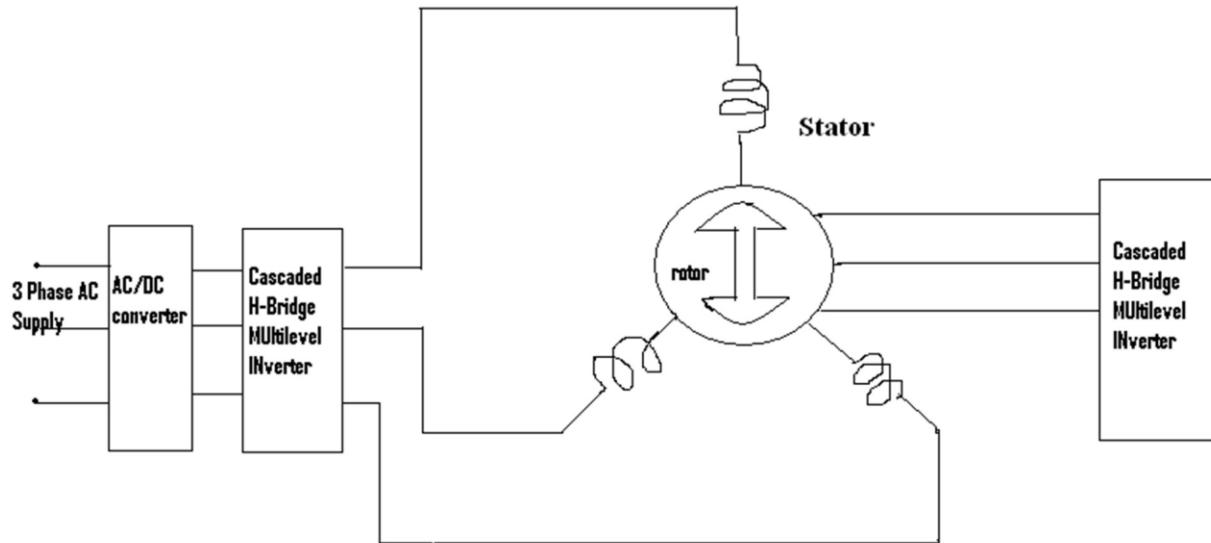

### 1.3 Dual Inverter fed Open end winding Induction Motor Drive

The drawbacks of the Multilevel Inverter can be overcome by feeding an Induction motor from both ends through two inverters with the removal of neutral point of stator. This configuration is called Dual Inverter fed Open End winding Induction Motor. The dual inverter has reduced switching loss and circuit complexity when compared to conventional two level inverter [9]. The output of this configuration has multiple levels thus reducing Total Harmonic Distortion. During the low speed operation of Induction motor, the multilevel inverters are having very high THD resulting in high heating losses, derating and noise. The effects are minimized by the dual inverter fed open end winding Induction motor drive. Figure 3 shows the Dual inverter fed open end winding induction motor.

Figure3 Dual inverter fed open end winding induction motor

#### 1.4 Comparison of MLI and DI

When the number of levels in the MLI is increased, the number of bridges is high and therefore large number of switches is used which leads to high switching losses and increased circuit complexity and cost. Whereas in Dual inverter, less number of bridges which has less number of switches gives reduced switching losses [10]. When the number of levels of Dual inverter is increased, it achieves reduced Total Harmonic Distortion when compared to MLI. The comparison for different output levels of MLI and DI is given in the Table 1. In Table 1 Number of bridges and number of switches has been given for MLI and DI for different output levels.

Table 1Comparison of MLI and DI

| Output Levels | No of Bridges       |               | No of Switches      |               |

|---------------|---------------------|---------------|---------------------|---------------|

|               | Multilevel Inverter | Dual Inverter | Multilevel Inverter | Dual Inverter |

| 3             | 3                   | 2             | 12                  | 12            |

| 5             | 6                   | 3             | 24                  | 18            |

| 7             | 9                   | 4             | 36                  | 24            |

| 9             | 16                  | 4             | 64                  | 24            |

This paper investigates the comparison of multilevel inverter and Dual Inverter fed open end winding Induction motor drive.

The scope of the paper can be summarized as follows:

- A simulation model of the MLI and DI will be developed.

- A simulation study on the operation and performance of the MLI and DI has to be carried out.

- Using MATLAB Simulink to simulate MLI and DI and the firing pulse has been generated using Space vector modulated technique in Embedded Matlab editor file

- Comparing the performance of the Dual Inverter with Cascaded H-Bridge multilevel inverter and results will be verified.

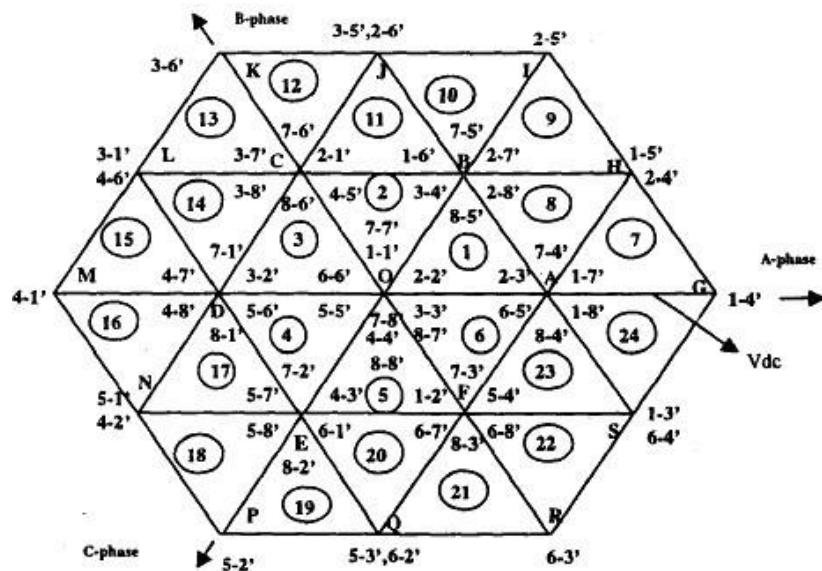

#### 2. Three level output of SVPWM Technique

The space phasor combinations from the two inverters are shown in Figure.4. In all 64 spaces phasor combinations are possible from both the inverters. For example, a combination 6-1' implies that the switching state for inverter- 1 is (+ - +) and that for inverter-2 is (+ - -). A '+' means top switch in the inverter is on, a '-' means

bottom switch in the inverter is on. The motor phase voltage can be found out from the pole voltages of individual inverters [11].

Separate DC supply is used for individual inverter to block the flow of third harmonic currents. This is achieved using isolated transformers in providing the DC supply for both the inverters.

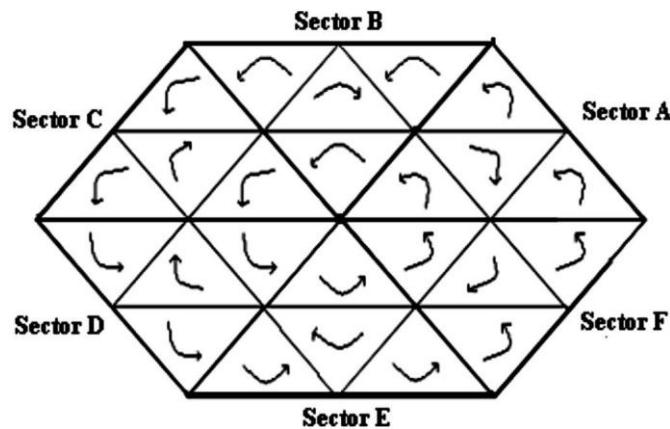

The 64 voltage space phasor locations form the vertices of 24 equilateral triangles, which are referred to as 24 sectors (Fig.4). Six adjacent sectors together form a hexagon. Six such hexagons can be identified with their centers located at A, B, C, D, E, and F respectively. In addition there is one inner hexagon with its center at O. Based on these sub-hexagons, a space phasor based PWM scheme is proposed in the same way as in the case of the conventional three phase inverter [13].

Figure4 Space phasor combination for three level output

The degrees of freedom we have in the choice of a given modulation algorithms are:

- The choice of the zero vector - whether we would like to use **V7** (111) or **V8** (000) or both.

- Sequencing of the vectors

- Splitting of the duty cycles of the vectors without introducing additional commutations.

The direction of the switching sequence for all the regions in the sector is shown in the Figure 5.

Figure5 Direction of the switching sequence for all regions in the sectors

## 2.1 Algorithm for SVPWM

### (i) Determination of time duration

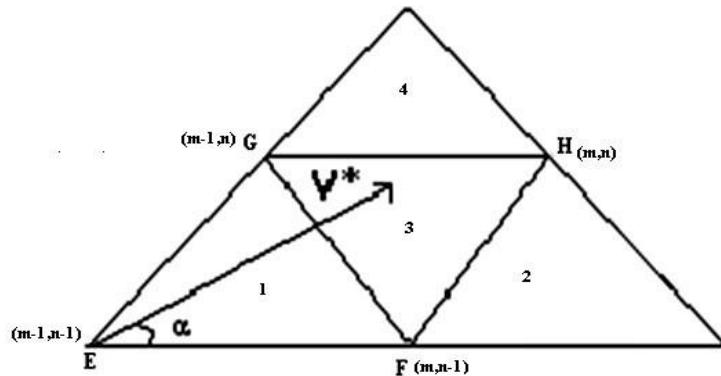

Figure6 Four regions in sector A

In the Figure 6 we can Identify two triangles

$\Delta EFG$  and  $\Delta FGH$

In triangle  $\Delta EFG$ ,

$$\triangleright \quad TF = (V_{rm} - (m-1))TS$$

$$\triangleright \quad TG = (V_{rm} - (n-1))TS$$

$$\triangleright \quad TE = TS - TF - TG$$

In triangle  $\Delta FGH$ ,

$$\triangleright \quad TG = (m - V_{rm})TS$$

$$\triangleright \quad TF = (n - V_{rm})TS$$

$$\triangleright \quad TH = TS - TG - TF$$

Where  $V_r$  is the reference vector,  $V_{rm}$  in  $m$ -axis and  $V_{rn}$  in  $n$ -axis.

$$V_{rm} = \left( \frac{2}{\sqrt{3}} \right) \left( \frac{MV_r}{V_{dc}} \right) \sin \left( \frac{\pi}{3} - \theta \right)$$

$$V_{rn} = \left( \frac{2}{\sqrt{3}} \right) \left( \frac{MV_r}{V_{dc}} \right) \sin (\theta)$$

### (ii) Determine switching states

By considering the switching transition of only one device at any time; the switching orders given below are obtained for each region located in Sector A if all switching states in each region are used. Therefore, switching signals for Sector A are;

In Sector A,  $\alpha$  is between  $0^\circ \leq \alpha < 60^\circ$ , four regions are specified sector 1, sector 7, sector 8, sector 9 from the Figure 4 and Figure 5. Similarly all the switching patterns of all the other sectors and the specified regions [14] are given in the Table 2

**Table 2 Switching sequence for three level combination of SVPWM**

| Inner sector number | Inverter 1 not switched ON | Inverter 2 not switched ON |

|---------------------|----------------------------|----------------------------|

| 1                   | 88'-84'-85'-87'            | 87'-27'-17'-77'            |

| 2                   | 88'-86'-85'-87'            | 87'-27'-37'-77'            |

| 3                   | 88'-86'-81'-87'            | 87'-47'-37'-77'            |

| 4                   | 88'-82'-81'-87'            | 87'-47'-57'-77'            |

| 5                   | 88'-82'-83'-87'            | 87'-67'-57'-77'            |

| 6                   | 88'-84'-83'-87'            | 87'-67'-17'-77'            |

| outer sector number | Inverter 1 not switched ON | Inverter 2 not switched ON |

| 7                   | 84'-14'-24'-74'            | 74'-24'-14'-84'            |

| 8                   | 85'-15'-65'-75'            | 75'-65'-15'-85'            |

| 9                   | 85'-15'-25'-75'            | 75'-25'-15'-85'            |

| 10                  | 85'-35'-25'-75'            | 75'-25'-35'-85'            |

| 11                  | 85'-35'-45'-75'            | 75'-45'-35'-85'            |

| 12                  | 86'-36'-26'-76'            | 76'-26'-36'-86'            |

| 13                  | 86'-36'-46'-76'            | 76'-46'-36'-86'            |

| 14                  | 81'-31'-21'-71'            | 71'-21'-31'-81'            |

| 15                  | 81'-31'-41'-71'            | 71'-41'-31'-81'            |

| 16                  | 81'-51'-41'-71'            | 71'-41'-51'-81'            |

| 17                  | 81'-51'-61'-71'            | 71'-61'-51'-81'            |

| 18                  | 82'-52'-42'-72'            | 72'-42'-52'-82'            |

| 19                  | 82'-52'-62'-72'            | 72'-62'-52'-82'            |

| 20                  | 83'-53'-43'-73'            | 73'-43'-53'-83'            |

| 21                  | 83'-53'-63'-73'            | 73'-63'-53'-83'            |

| 22                  | 83'-13'-63'-73'            | 73'-63'-13'-83'            |

| 23                  | 83'-13'-23'-73'            | 73'-23'-13'-83'            |

| 24                  | 84'-14'-64'-74'            | 74'-64'-14'-84'            |

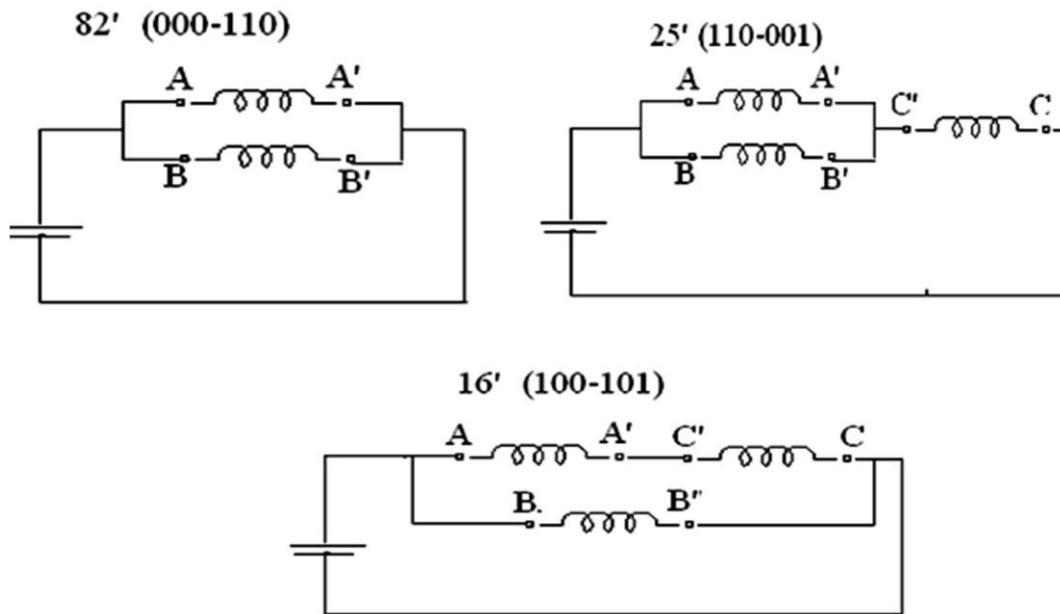

The SVM Switching sequence for three level dual inverter has been developed in two different combinations. In dual inverter, inverter 1 and inverter 2 are connected. First mode is Inverter 2 is clamped. (Inv.2 is clamped and Inv.1 is ON), [17].Second mode is Inverter 1 and Inverter 2 is ON. The different modes of result are presented below.Figure 7 Equivalent circuits for the switching states of the dual inverter.

Figure 7 Equivalent circuits for the switching states of the dual inverter

### 3. Simulation Results

The Simulation model for the Dual Inverter IM, the firing pulses of different levels are presented. Space vector modulated technique has been developed. Space vector modulation technique is used to generate pulses for the inverters. Simulation results for different combination for three level output waveform for inverter and motor phase winding are presented. Simulation results for five level output waveforms are also shown for different layers. The Spectrum waveform for different levels has been given. Comparison of different levels for Dual Inverter and Multilevel Inverter results are presented.

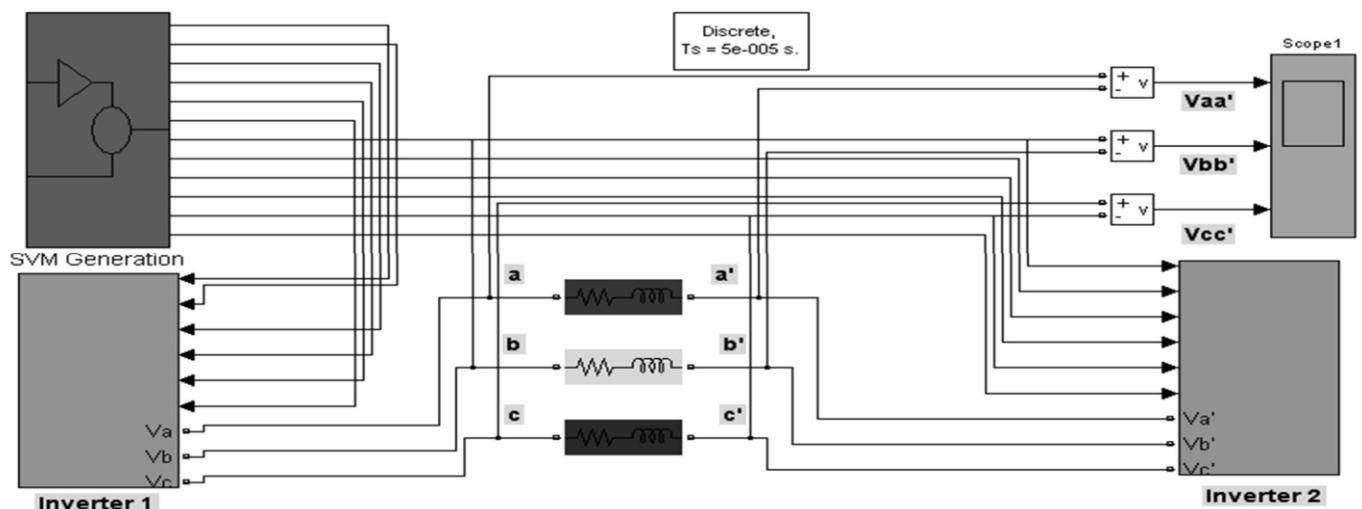

#### 3.1 Simulink Model of Dual Inverter Fed Open End Winding Induction Motor Drive

The simulink model of the Dual Inverter is shown in the Figure 8. In the Figure 8 the block Inverter 1 and Inverter 2 is a two level three phase inverter which is connected to the load on both the ends. This configuration is called Dual Inverter. The Induction motor is acting as a balanced load. The SVM generation block is shown in the Figure 9. When increasing the number of bridges on both the sides gives reduced THD.

Figure 8 Simulink model of Dual Inverter

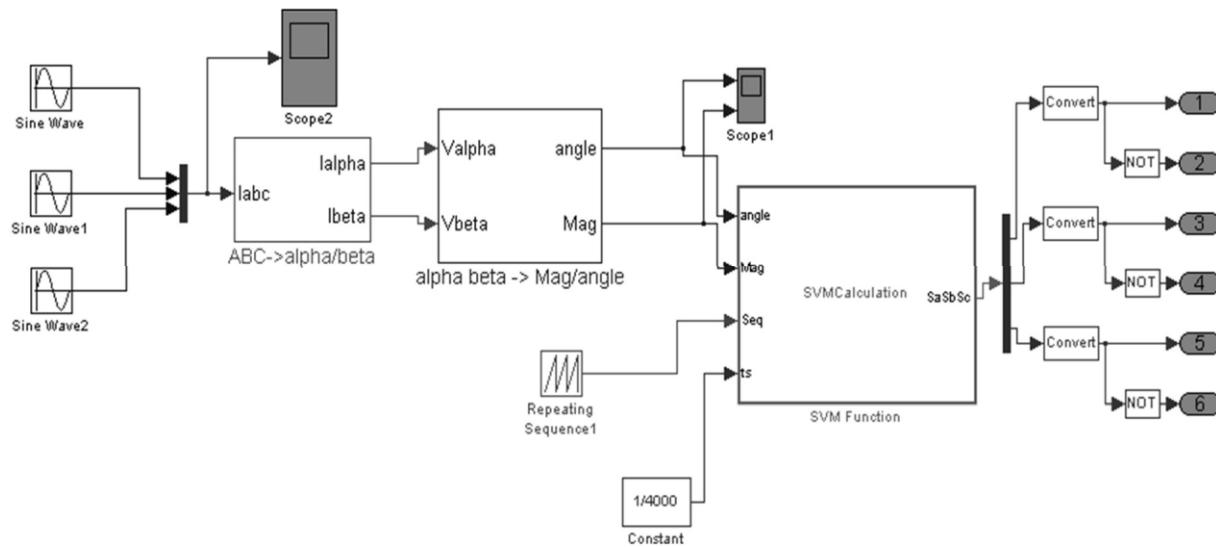

### 3.2 Simulink Model of Space Vector Pulse Width Modulation Technique

The SVM generation technique is shown in the Figure 9. The sine reference wave for three phase is the input for SVM generation. The three phase to two phase is converter using Park Transform function. This alpha/beta is taken as magnitude and angle format and applied to the SVM calculation. The carrier wave is also applied to the SVM calculation, the carrier wave used in repeating sequence or triangular form. The SVM calculation block shown in the fig. 9 is embedded matlab editor file, where the program for SVM technique is formulated and interfaced with simulink block. The firing pulses are generated using SVM algorithm and fed to the respective switches of Dual Inverter.

Figure 9 Equivalent circuits for the switching states of the dual inverter

### 3.3 Simulation Results for three level output of Dual Inverter

The Simulink model of dual inverter fed open end winding induction motor drive and Space vector modulation technique are presented.

Simulation is carried out under two output modes:

- 1) Inverter 2 clamped and Inverter 1 ON are assumed as  $V_{dc}/2=270V$  for an individual inverter ( $V_{dc}=540V$ ).

- 2) Inverter 1 and Inverter 2 both ON are assumed as  $V_{dc}/2 =310 V$  for an individual inverter ( $V_{dc}=620V$ ).

The output voltages of each bridges and across the windings are observed and presented in the Figure 10a, 10b, 10c and 10d respectively.

The motor parameters used for simulation are

- 1.5 Hp, 220V, 50 Hz, 4 pole.

- $R_s=4.495 \text{ Ohm}$

- $R_r'=5.365 \text{ Ohm}$

- $X_{ls}=0.165\text{H}$

- $X_r'=0.149\text{H}$

### 3.4 Simulation Results for the mode Inverter 2 Clamped and Inverter 1 ON

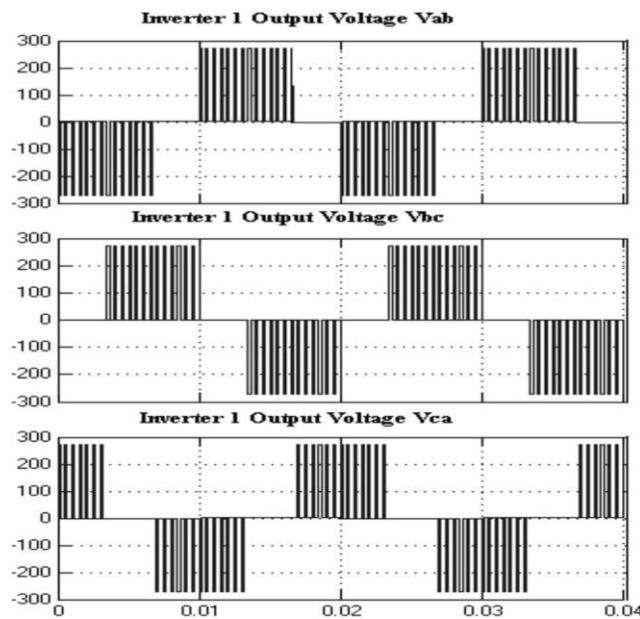

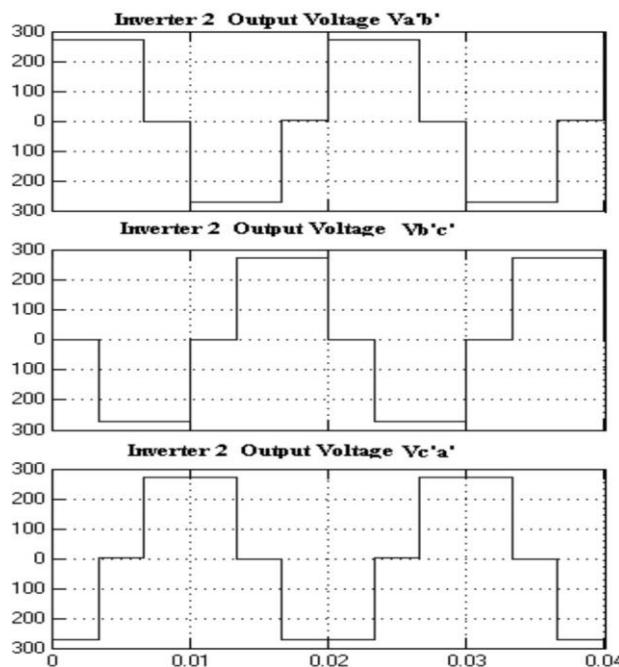

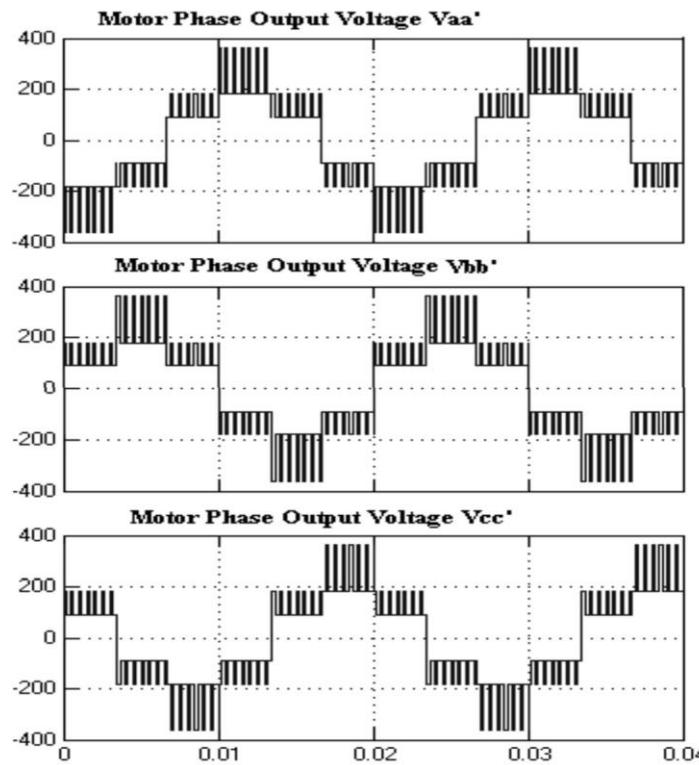

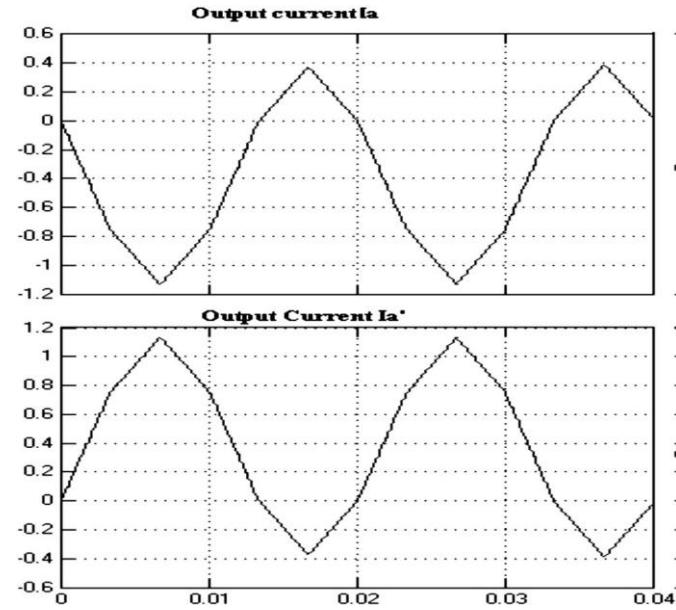

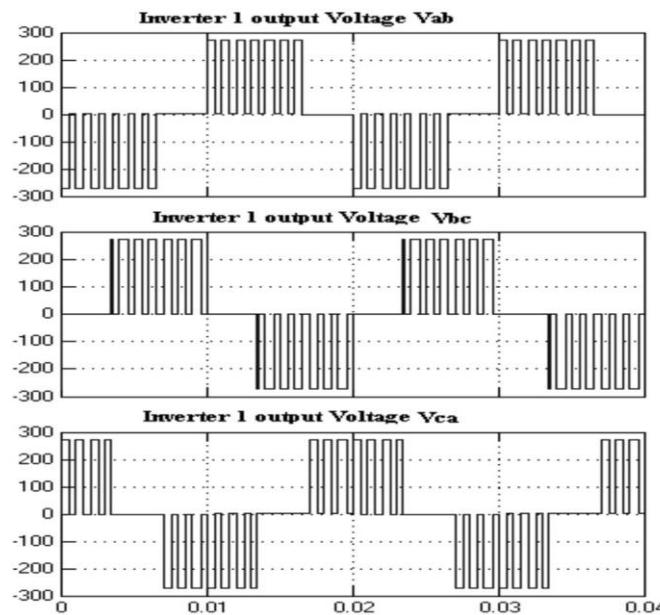

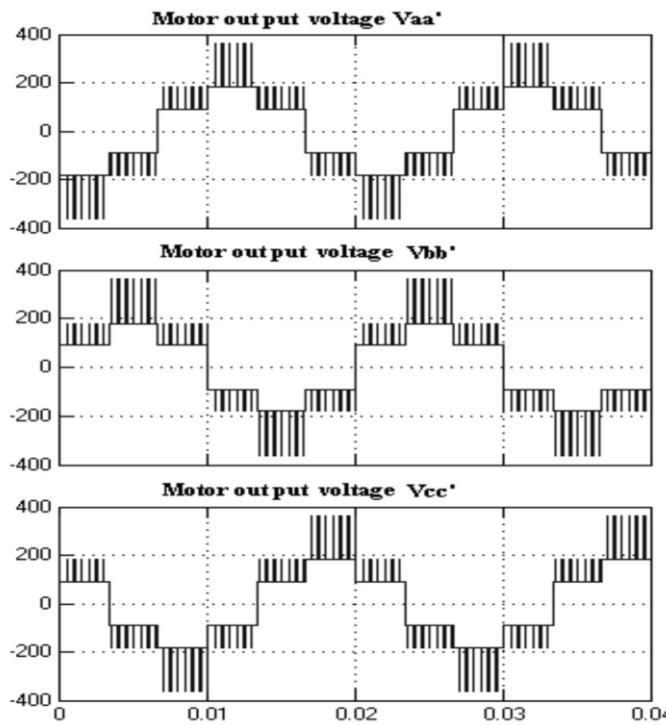

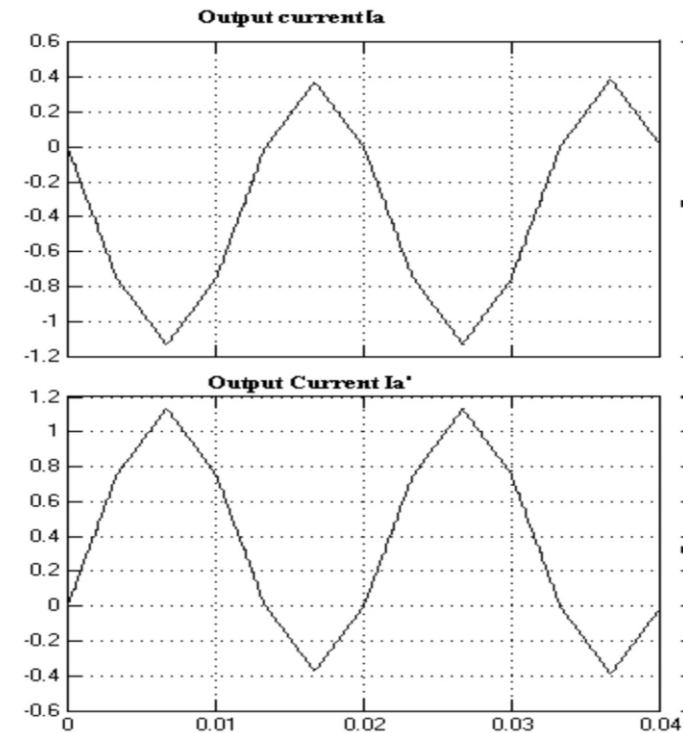

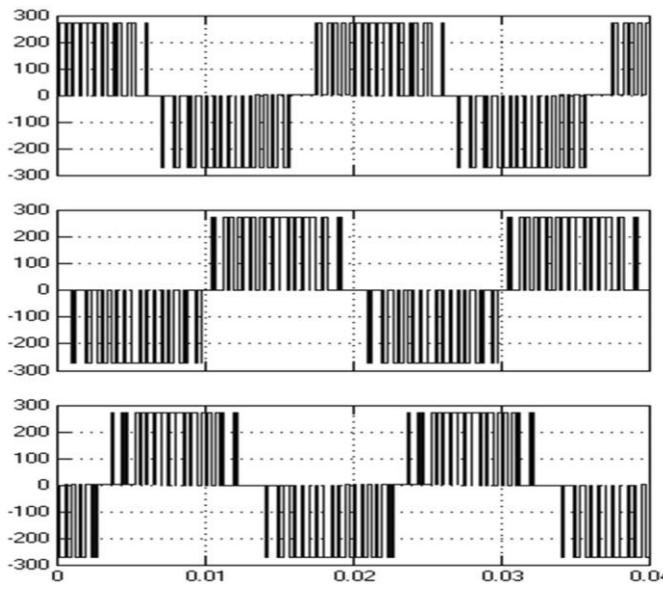

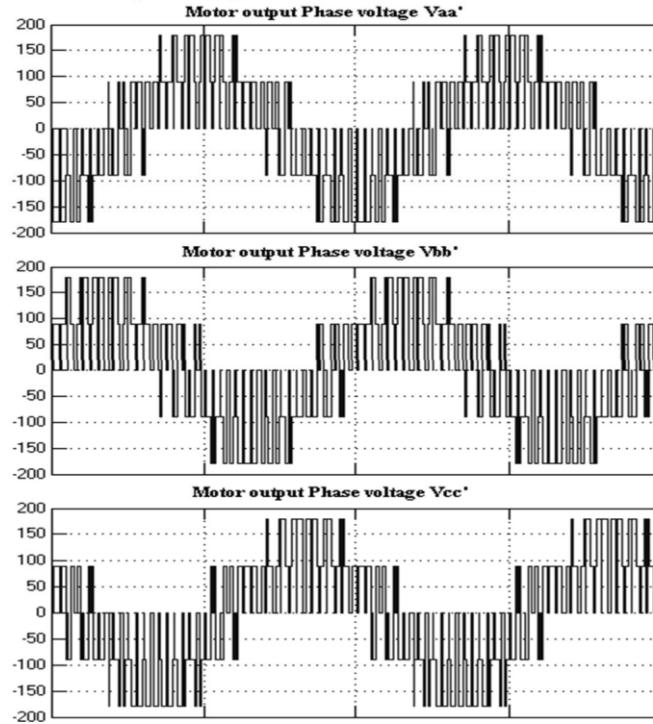

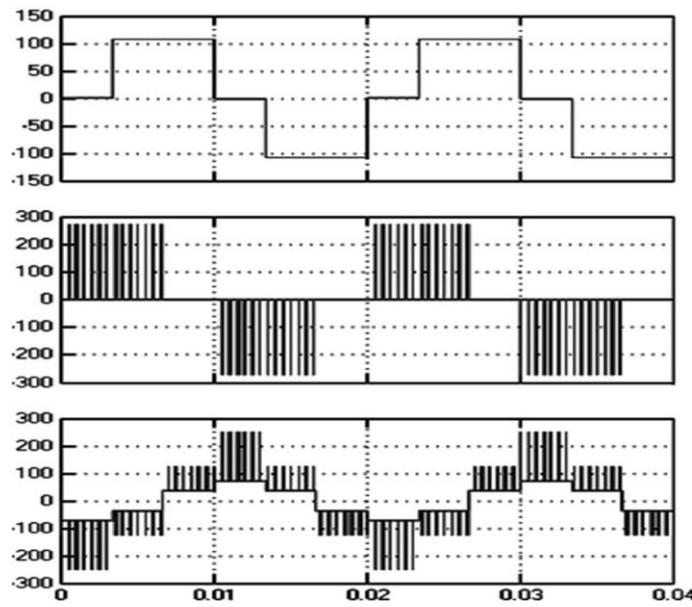

It is seen that the output voltage of Inverter 1 has two levels shown in the Figure 10a and Inverter 2 has two levels but in clamped shown in the Figure 10b and across the motor winding has three level output shown in the Figure 10c. The output current waveform for three level output is shown in the Figure 10d. When the input is given to both the inverters is 270 V each. The switching frequency applied is 1KHz

Figure10a: Inverter1 output voltage Vab, Vbc, Vca for Modulation Index =0.9

Figure10b : Inverter 2 output voltage Va'b', Vb'c', Vc'a' for Modulation Index=0.9.

Figure10c Motor Phase voltage  $V_{aa}'$ ,  $V_{bb}'$ ,  $V_{cc}'$  for Modulation Index=0.9.Figure10d Output Current  $I_a$  and  $I_{a'}$  for Modulation Index=0.9.

In the first mode the net output voltage from the motor is 214.6 V, Inverter 1 output voltage is 110V, Inverter 2 output voltage is 220 V.

### 3.4 Simulation Results for the combination Inverter 1 and Inverter 2 ON

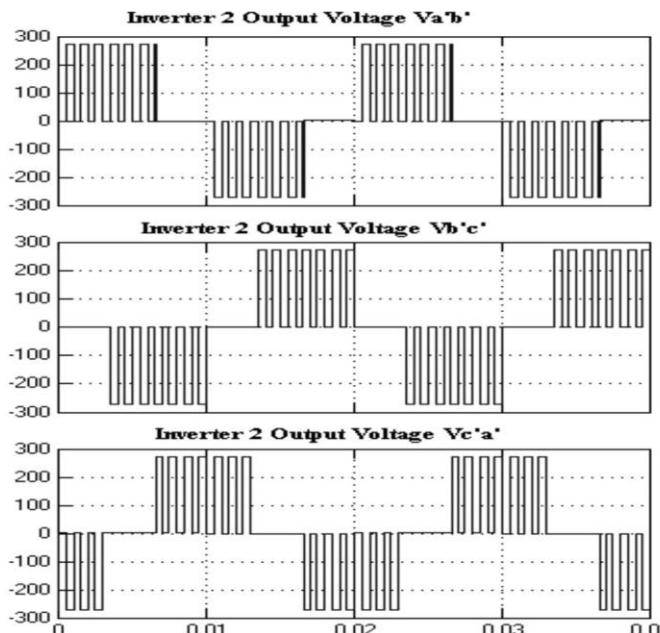

It is seen that the output voltage of Inverter 1 has two levels shown in the Figure 11a and Inverter 2 has two levels but in clamped shown in the Figure11b and across the motor winding has three level output shown in the Figure11c.The output current waveform for three level output is shown in the Figure11d.When the input is given to both the inverters is 270 V each. The switching frequency applied is 1 KHz.

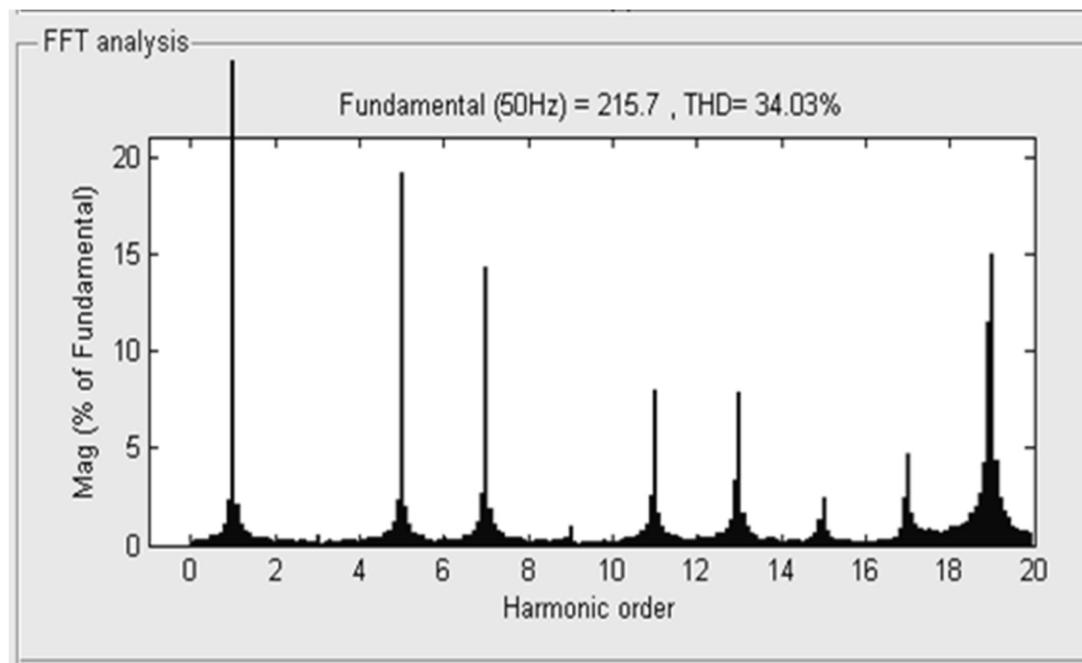

In the second mode the net output voltage across the motor is 216.8 V, Inverter 1 output voltage is 187 V, Inverter 2 output voltage is 187 V.The THD for two mode of three level output is 34.03%

Figure 11a: Inverter1 output voltage Vab, Vbc, Vca for Modulation Index=0.9.

Figure11b Inverter 2 output voltage Va'b', Vb'c', Vc'a' for Modulation Index=0.9.

Figure 11c Motor Phase voltage  $V_{aa'}$ ,  $V_{bb'}$ ,  $V_{cc'}$  for Modulation Index=0.9.Figure 11d: Output Current  $I_a$  and  $I_{a'}$  for Modulation Index=0.9.

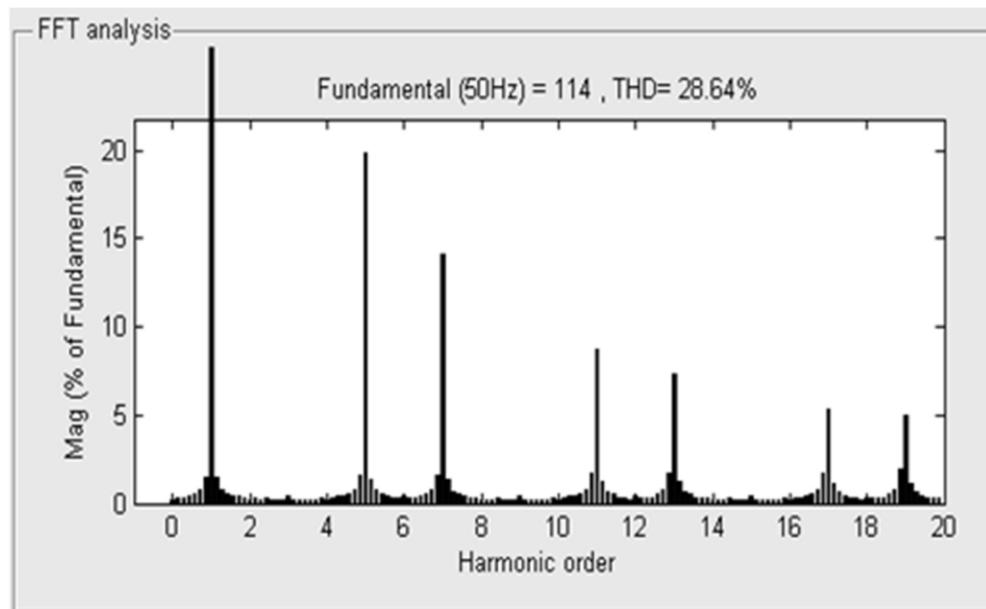

The spectrum output waveform for three level output combination is shown in the Figure 12

Figure12 Spectrum waveform for three level output

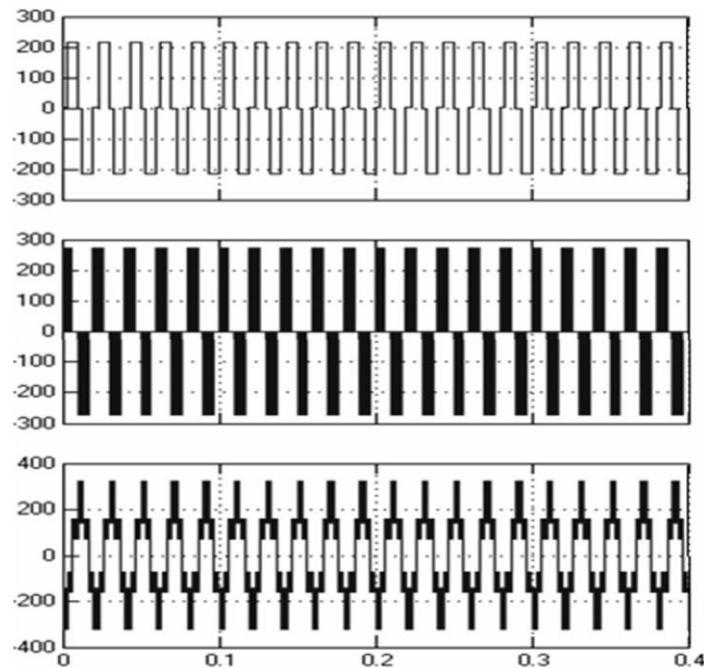

### 3.5 Simulation Results for five level output

The input voltages for different layers for five level :

- Layer 1, 1 to 6 sectors gives the two level output waveform

- Layer 2, 1 to 24 sectors gives the three level output waveform.

- Layer 3, 1 to 54 sectors gives the three level output waveform.

- Layer 5 , 1 to 150 sectors gives the five level output waveform

Firing pulses are generated for a inverter 1&2 cascaded and inverter 3, and fed to the open end winding induction motor. The output voltages of inverter 1&2 cascaded and inverter 3, Motor phase voltages and currents for modulation index=0.9 are observed and shown in the Figure 13a and13b.

### 3.6 Simulation results for layer 1 in five level output

The layer 1 of the five level output is observed and the output voltages of inverter 3, Motor phase voltages and currents for modulation index(MI)=0.9 are observed and shown in the Figure13a and13b.

Figure13a Inverter 3 output voltage  $V_{a'b'}$ ,  $V_{b'c'}$ ,  $V_{c'a'}$  for Modulation Index=0.9Figure13b Motor Phase voltage  $V_{aa'}$ ,  $V_{bb'}$ ,  $V_{cc'}$  for Modulation Index=0.9.

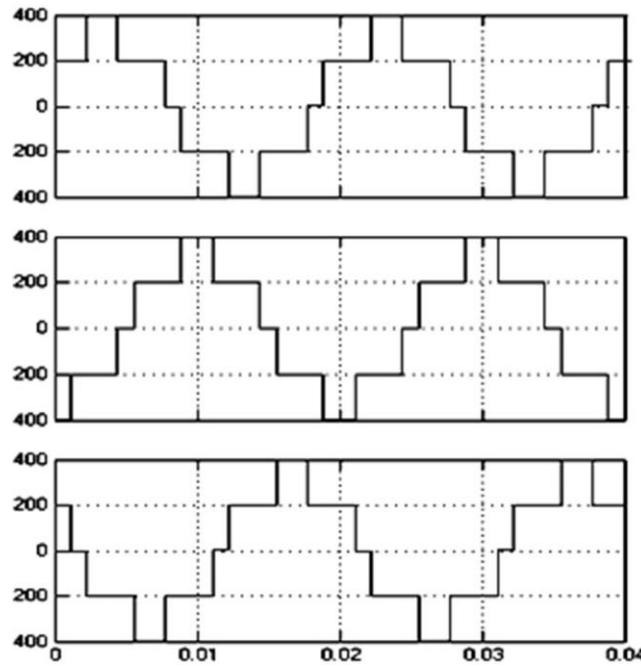

### 3.7 Simulation results for layer 3 & 5

The layer 3 and layer 5 of the five level output is observed and the output voltages of inverter 1 & 2 cascaded and inverter 3, Motor phase voltages and currents for modulation index(MI)=0.9 are observed and shown in the Figure14 andFigure15 respectively.

Figure14 Output waveform for layer 3

Figure15 output waveform for layer 5

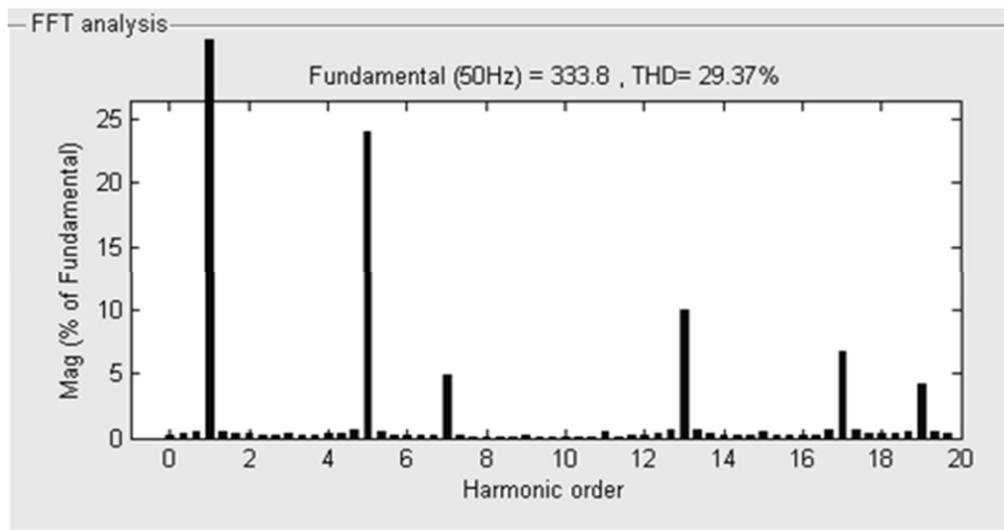

The spectrum output waveform for five level output combination is shown in the Figure 16.

Figure16 Spectrum waveform for three level output

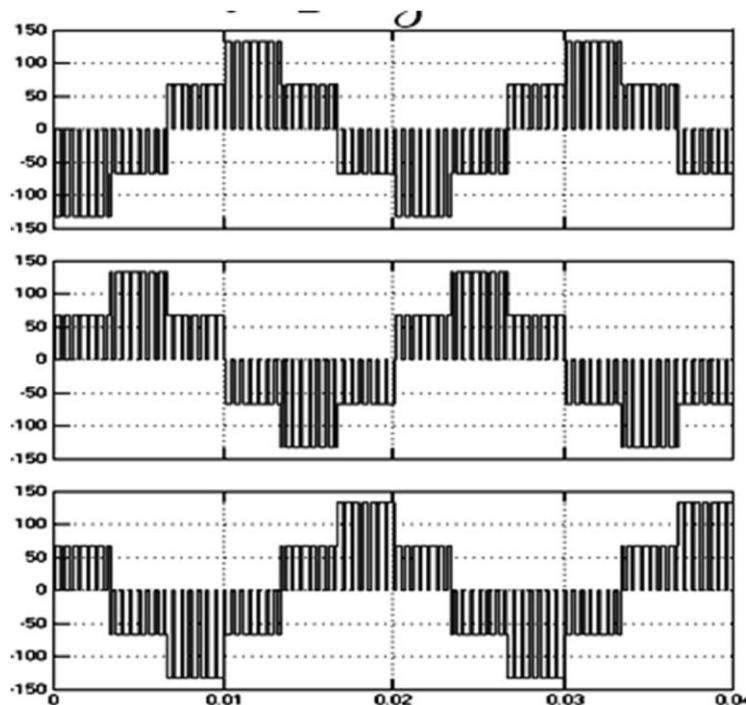

### 3.8 Simulation Results for Three level Cascaded H-bridge inverter:

(i) Three level output voltage waveform for Cascaded H-bridge inverter

Figure17 Output voltage waveform for three level

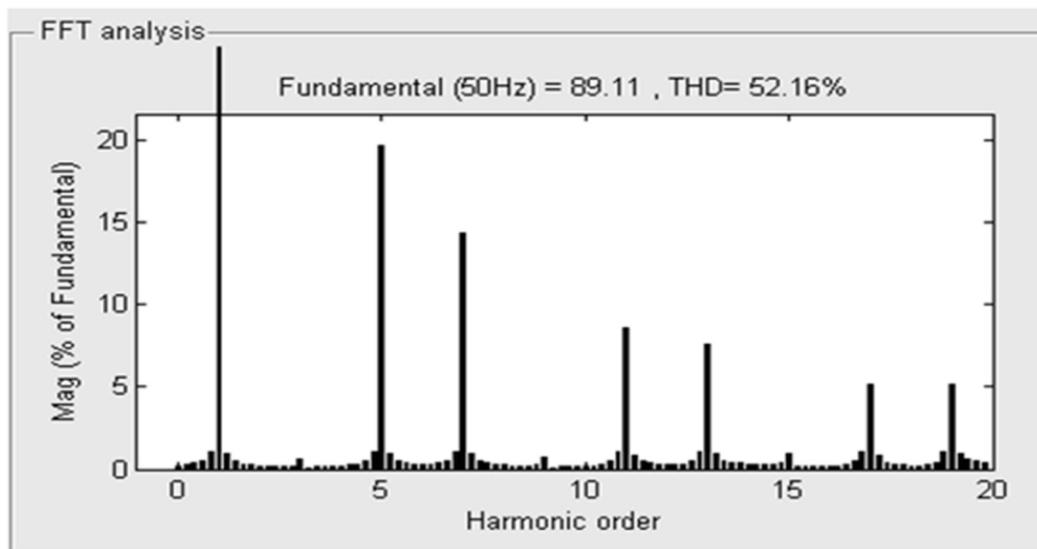

(ii) Spectrum waveform for three level Cascaded H-bridge inverter

Figure18 Spectrum waveform for three level

### 3.9 Simulation Results for five level Cascaded H-bridge inverter: Five level output voltage waveform for Cascaded H-bridge inverter

Figure19 Output voltage waveform for five level

### 3.10 Spectrum waveform for five level Cascaded H-bridge inverter

Figure20 Spectrum waveform for five level.

### 3.11 Comparison of THD for Dual Inverter and Multilevel Inverter

The THD is compared for Dual Inverter and Multilevel Inverter is given in the Table 3. It has been observed that THD for 3 level output to DI is 34.03 % and THD for 3 level output to MLI is 52.16%. The THD for 5 level output to DI is 28.64% and THD for 5 level to MLI is 30.37%.

Table 3 Comparison of DI and MLI

| No of Levels | THD for Dual Inverter | THD for Cascade H- bridge |

|--------------|-----------------------|---------------------------|

| 3 level      | 34.03                 | 52.16                     |

| 5 level      | 28.64                 | 30.37                     |

## 4. CONCLUSION

The performance investigation approach for Multilevel inverter and Dual Inverter using Space vector pulse width modulation technique is modeled using Simulink/Matlab environment. A novel switching technique using the Embedded Matlab editor results in a higher magnitude of fundamental output voltage available as compared to the sinusoidal PWM. A simulation model of the SVPWM scheme has been developed in the Embedded Matlab Editor and the generated firing pulses are applied to the Multilevel Inverter fed induction motor drive and Dual Inverter fed open end winding induction motor drive. As a consequence, as the number of bridges on both sides of the Dual Inverter increases, the THD decreases with fewer switches compared to the Multilevel Inverter. It has been observed that THD for 3-level output to DI is 34.03 % and THD for 3-level output to MLI is 52.16 %. THD for 5-level output to DI is 28.64 % and THD for 5-level to MLI is 30.37 %.

## REFERENCES

- [1] Nabae, I. Takahashi, and H. Akagi, "A new neutral point-clamped PWM inverter," *IEEE Trans. Ind. Appl.*, vol. IA-17, no. 5, pp. 518–523, Sep. 1981

- [2] J.-S. Lai and F. Z. Peng, "Multilevel converters—A new breed of power converters," *IEEE Trans. Ind. Appl.*, vol. 32, no. 3, pp. 509–517, May/Jun. 1996.

- [3] R.W. Menzies, P. Steimer, and J. K. Steinke, "Five-level GTO inverters for large induction motor drives," *IEEE Trans. Ind. Appl.*, vol. 30, no. 4, pp. 938–944, Jul./Aug. 1994.

- [4] G. Sinha and T. A. Lipo, "A four level inverter based drive with a passive front end," *IEEE Trans. Power Electron.*, vol. 15, no. 2, pp. 285–294, Mar. 2000.

- [5] S.Daher,J.Schmid, and F.L.M.Antunes, "Multilevel inverter topologies for stand-alone PVsystems," *IEEE Trans. Ind. Electron.*, vol. 55, no. 7, pp. 2703–2712, Jul. 2008.

- [6] M. R. Baiju, K. K. Mahapatra, R. S. Kanchan, and K. Gopakumar, "A dual two-level inverter scheme with common-mode voltage elimination for an induction motor drive," *IEEE Trans. Power Electron.*, vol. 19, no. 3, pp. 794–805, May 2004.

- [7] V. T. Somasekhar, K. Gopakumar, M. R. Baiju, K. K. Mohapatra, and L. Umanand, "A multilevel inverter system for an induction motor with open-end windings," *IEEE Trans. Ind. Electron.*, vol. 52, no. 3, pp. 824–836, Jun. 2005

- [8] Sidney R. Bowes and Yen-Shin Lai, "The Relation between Space-Vector Modulation and Regular-Sampled PWM", *IEEE Trans. Industrial Electronics.*, vol. 44, no. 5, Oct. 1997, pp. 670 – 679.

- [9] Fei Wang, "Sine-Triangle versus Space- Vector Modulation for Three-level PWM voltage Source Inverters", *IEEE Trans. Ind. Applicat.*, vol. 38, no. 2, Mar/Apr 2002 pp. 500-506.

- [10] R. S. Kanchan, M. R. Baiju, K. K. Mohapatra, P. P. Ouseph, and K. Gopakumar, "Space vector PWM signal generation for multilevel inverters is using only the sampled amplitudes of reference phase voltages," *Proc. Inst. Elect. Eng.—Electr. Power Appl.*, vol. 152, no. 2, pp. 297–309, Mar. 2005.

- [11] P.N.Tekwani, R.S.Kanchan, and K.Gopakumar, "A dual five-level inverter-fed induction motor drive with common-mode voltage elimination and dc-link capacitor voltage balancing using only the switching-state redundancy: Part I," *IEEE Trans. Ind. Electron.*, vol. 54, no. 5, pp. 2600–2608, Oct. 2007.

- [12] P.N.Tekwani, R.S.Kanchan, and K.Gopakumar, "A dual five-level inverter-fed induction motor drive with common-mode voltage elimination and dc-link capacitor voltage balancing using only the switching-state redundancy: Part II," *IEEE Trans. Ind. Electron.*, vol. 54, no. 5, pp. 2609–2617, Oct. 2007.

- [13] S. Kanchan, P. N. Tekwani, and K. Gopakumar, "Three level inverter scheme with common mode voltage elimination and dc link capacitor voltage balancing for an openend winding induction motor drive", *IEEE Transactions on Power Electronics*, "vol.21, no.6, pp. 1676-1683", November, 2006, USA.

- [14] Aneesh Mohamed A. S., AnishGopinath, and M. R. Baiju, *Member, IEEE*, "A Simple Space Vector PWM Generation Scheme for Any General  $n$ -Level Inverter". *IEEE transactions on industrial electronics*, vol. 56, no. 5, may 2009.

- [15] K.Chandrasekhar, G.Tulasi Ram Das, "An Eight-level Inverter System for an Inductior Motor with Open-end Windings", in *Proceedings of the 2005 IEEE –PEDS Conference*, pp.219-223.

- [16] K.Chandrasekhar and G.Tulasi Ram Das, "A Nine-Level Inverter System for an Open-End Winding Induction Motor Drive ", *Proc.IEEE Conf. –ICIEA-2006*, pp.1-6.

- [17] V.T.Somasekhar, K.Gopakumar, M.R.Baiju and K.K.Mohapatra, "A Multilevel Inverter system for an Induction Motor with Open-end Winding" *IEEE Trans. Ind. Electronics*, 2005, pp.824-836.